| Frequenza di eccitazione 50 Hz, 400 Hz e 2,6 kHz |  |

| Risoluzione: 10 bit, 12 bit, 14 bit | |

| Alta velocità di tracciamento | |

| L'ingresso non standard è regolabile tramite resistenza esterna o regolato sul terminale di ingresso del prodotto | |

| Uscita in tensione CC direttamente proporzionale alla velocità angolare | |

| Compatibile con la serie SDC1700 dell'azienda americana AD |

conversione. | La potenza operativa è di ±15 V e + 5 V CC. Ci sono due tipi di |

segnale di uscita: sincro a tre linee e segnale di riferimento (convertitore SDC) | |

o resolver a quattro linee e segnale di riferimento (convertitore RDC); L'output | |

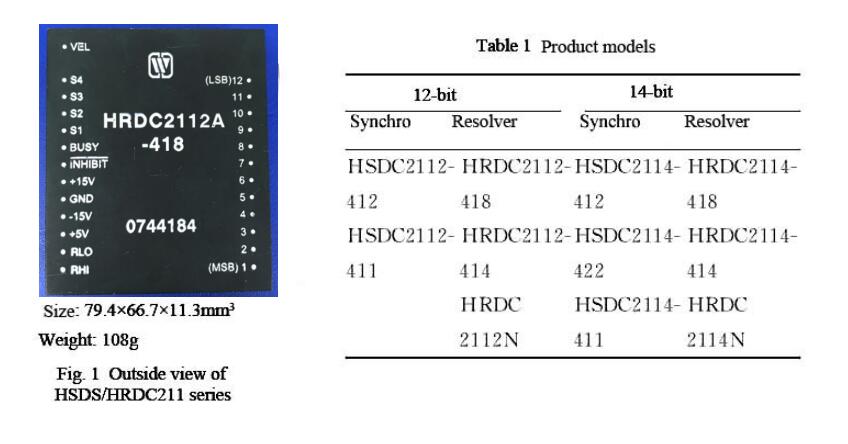

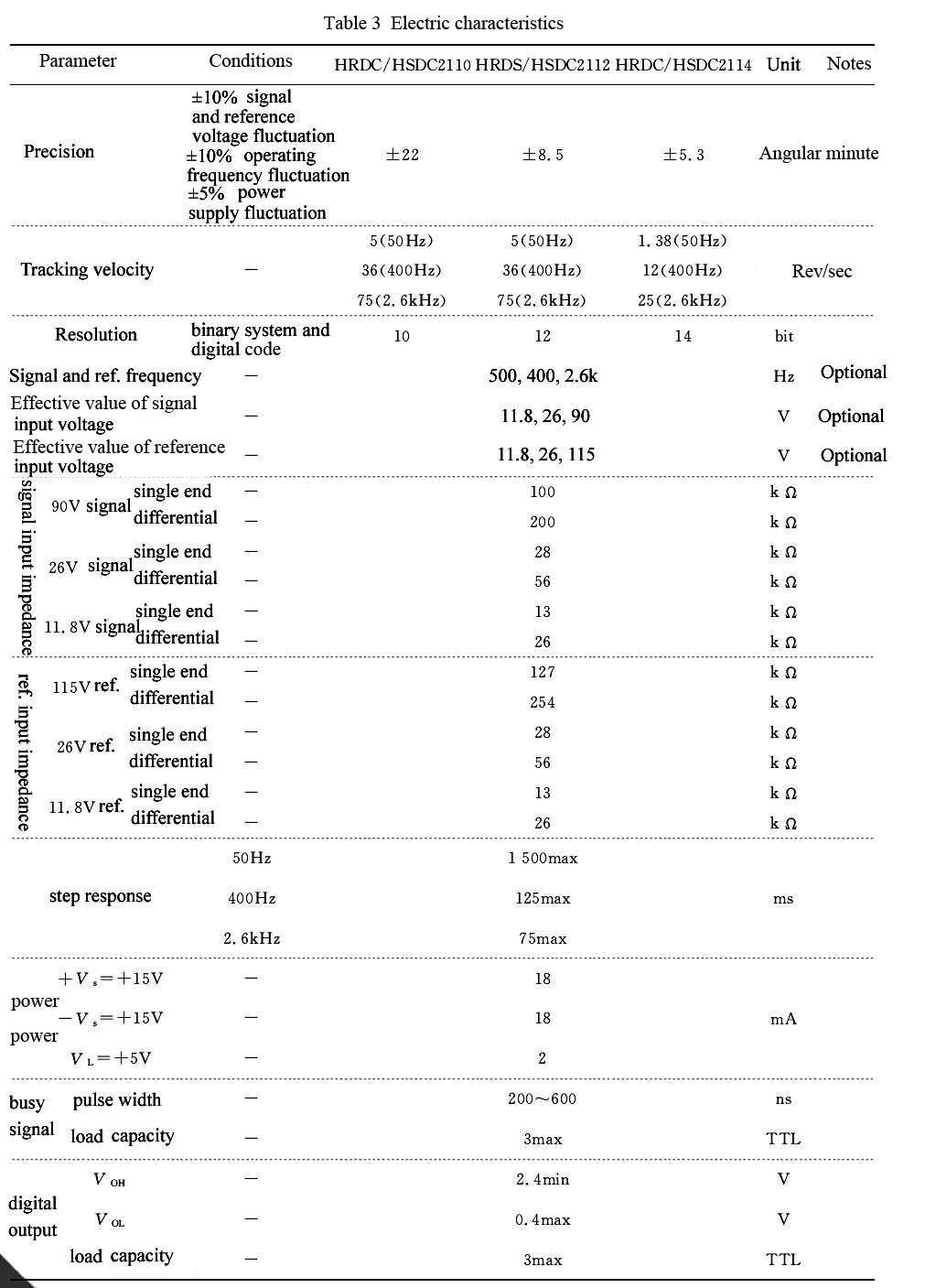

è codici digitali paralleli del sistema binario. | 4 Prestazioni elettriche (Tabella 2, Tabella 3) di Synchro to |

Convertitori digitali o da resolver a convertitori digitali (HSDC/HRDC211 | |

Serie) | |

Tabella 2 Condizioni nominali e condizioni operative consigliate | |

Massimo assoluto valore nominale | |

Tensione di alimentazione Vs: ± 17,5V |

| Valore effettivo della tensione di riferimento VRef: 11.8V, 26V, 115V Valore effettivo della tensione di riferimento V1*: 11,8V, 26V, 90V |  Frequenza di riferimento f*: 50 Hz, 400 Hz, 2,6 kHz |

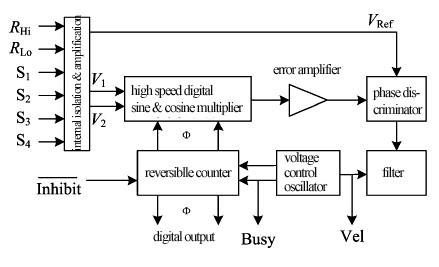

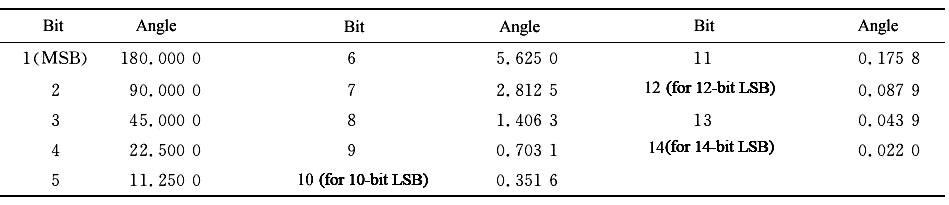

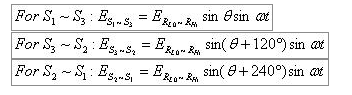

Dove, θ è l'angolo di ingresso analogico Il segnale ortogonale viene moltiplicato per l'angolo digitale binario φ nel Il segnale ortogonale viene moltiplicato per l'angolo digitale binario φ nel | contatore interno reversibile nel moltiplicatore della funzione seno-coseno e |

θ-φ≠0, l'oscillatore controllato in tensione emetterà un impulso per cambiare il | dati nel contatore reversibile, fino a quando θ-φ diventa zero all'interno del |

|  |

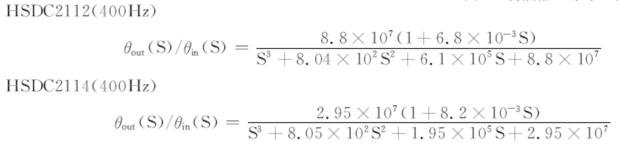

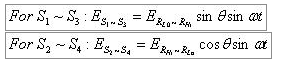

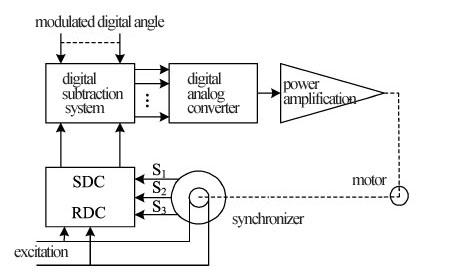

| precisione del convertitore, durante questo processo, il convertitore segue il cambiamento continuo dell'angolo di input θ. Per il principio di funzionamento, vedere la Fig. | 2. Funzione di trasferimento: di seguito sono riportati i parametri per la funzione di trasferimento di HSDC2112 e HSDC2114(400Hz), per altri modelli contattare il direttamente dal produttore. Fig.2 Schema a blocchi del principio di funzionamento del convertitore |

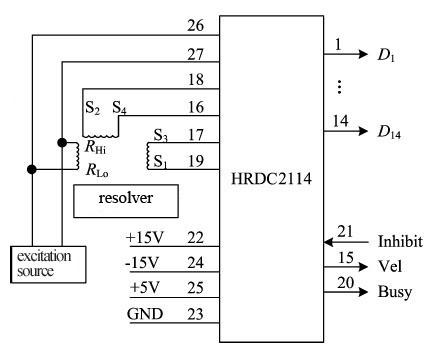

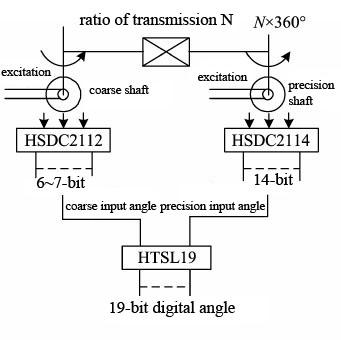

Esistono due metodi per leggere i dati validi del convertitore come segue: | Metodo di inibizione (lettura sincrona): | Imposta Inhibit su "0" logico, a questo punto il convertitore interromperà il monitoraggio. Aspettare | 1μs fino a quando i dati di output non sono stabili, leggi i dati, i dati letti sono i | valido in questo momento (1μs è stato ritardato). Impostato su "1" logico, a questo punto, il convertitore inizierà di nuovo a tracciare per prepararsi alla lettura dei successivi dati validi. | Metodo occupato (lettura asincrona):Inhibit |

1 | D1 | In modalità di lettura asincrona, | 15 | è impostato su “1” logico o vacante, se il loop interno è sempre stabile | stato o se i dati di uscita sono validi deve essere determinato tramite il |

2 | D2 | stato del segnale di occupato Occupato. Quando il segnale di occupato è ad alto livello, esso | 16 | S4 | indica che i dati sono in corso di conversione e i dati in questo momento lo sono |

3 | D3 | instabile e non valido; quando il segnale di occupato è a basso livello, indica il | 17 | S3 | la conversione dei dati è stata completata e i dati in questo momento sono stabili |

4 | D4 | e valido. In modalità di lettura asincrona, l'uscita Occupato è un treno di impulsi di | 18 | S2 | Livello TTL, la larghezza tra è correlata alla velocità di rotazione. Fare riferimento a |

5 | D5 | diagramma della sequenza temporale del trasferimento dei dati Fig. 3. | 19 | S1 | Fig.3 Sequenza temporale del trasferimento dei dati |

6 | D6 | (2) Metodo di attenuazione del segnale di ingresso | 20 | Se il synchro o il resolver utilizzato dall'utente non è standard, al fine di | fare in modo che la tensione del segnale di ingresso e la tensione di eccitazione in ingresso corrispondano a |

7 | D7 | valori nominali del convertitore, l'utente può adottare il metodo di | 21 |

| resistenza di attenuazione esterna collegata in serie, ovvero per ogni 1V |

8 | D8 | superando il valore nominale, collegare in serie una resistenza da 1,1kΩ al | 22 | terminale di ingresso corrispondente. Quando si utilizza il convertitore, la serie | la resistenza a ciascun terminale deve essere accuratamente selezionata e fornita, |

9 | D9 | e materiale di resistenza dello stesso lotto deve essere adottato in modo da garantire | 23 | la precisione di conversione del convertitore all'interno dell'ampia temperatura | range, per ogni 0,1% l'errore di corrispondenza della resistenza in serie sarà |

10 | generare un errore di conversione del minuto angolare di 1,7. | Si raccomanda dal produttore che sia preferibile avvisare | 24 | il produttore di personalizzare il synchro o il resolver non standard come | per i parametri richiesti quando l'utente li utilizza. |

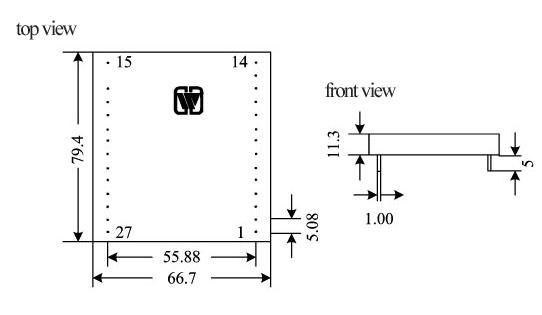

11 | 6 Curva MTBF (Fig. 4) di convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC211) | 7 Designazione dei pin (Fig. 5, Tabella 4) dei convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC211) | 25 | Fig. 4 Curva della temperatura MTBF | (Nota: secondo GJB/Z299B-98, buone condizioni del terreno previste) |

12 | Appunti: | ① la struttura di cui sopra è adatta per HRDC2114 | 26 | ② per SDC, nessun pin S4 | ③ per dispositivo a 12 bit, nessun pin 13 e 14, per dispositivo a 10 bit, nessun pin 11, 12, 13 e 14. |

13 | Fig.5 Designazione dei pin (vista dall'alto) | Tabella 4 Designazione dei pin | 27 | Spillo | Simbolo |

14 | Funzione | Spillo |

| Ingresso del segnale Uscita digitale di bit 6 Impegnato Ingresso segnale di occupato |  |

| Uscita digitale di bit 7 |

| -15V |  -Alimentazione 15V |

D11 |

|  |

| Alimentazione +5V | D12 |

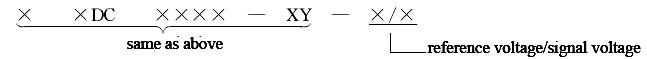

X

X