| Conversione dell'isolamento differenziale interno |  |

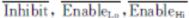

| Risoluzione a 16 bit | |

| Precisione: 2 minuti angolari | |

| Uscita latch a tre stati | |

| Elevata velocità di tracciamento continuo | |

| Pacchetto DDIP sigillato in metallo resistente alla nebbia salina a 36 fili | |

| Pin-to-pin compatibile con il modello SDC14560 dell'azienda DDC |

| dispositivo di conversione integrato per il tracciamento continuo progettato sul | principio del servo modello II. Questa serie di prodotti sono progettati e |

| prodotto dal processo MCM, gli elementi principali adottano un chip speciale | |

| sviluppato indipendentemente dal nostro istituto. La disposizione dei perni è | |

| compatibile con i prodotti della serie SDC14560 dell'azienda americana DDC, a 16 bit | |

| uscita di blocco dati in codice binario naturale parallelo, DIP a 36 linee totalmente | |

| pacchetto di metallo sigillato, presenta i vantaggi di alta precisione, piccolo | |

| volume, basso consumo energetico, leggerezza e alta affidabilità ecc., | e può essere ampiamente utilizzato in importanti armi strategiche e tattiche come |

| aerei, navi militari, cannoni, missili, radar, carri armati, ecc. | |

| 4. Prestazioni elettriche (Tabella 1, Tabella 2) | |

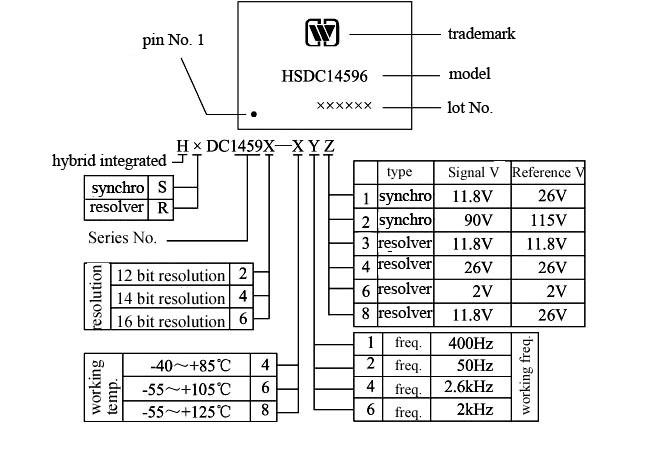

| Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1459) | |

| Tabella 1 Condizioni nominali e condizioni operative consigliate | |

| Assoluto max. valore valutato |

| Segnale tensione V1: valore nominale ±20% | Tensione di riferimento VRef: valore nominale ±20% | Frequenza operativa f: valore nominale ±20% | |

| Temperatura di conservazione Tstg: -65~150 ℃ | Condizioni Operative Raccomandate | ||

| Tensione di alimentazione logica VL: 5±0,5 V | Tensione di alimentazione Vs: 15± 0,75 V | ||

| Segnale tensione V1: valore nominale ±10% | Tensione di riferimento VRef: valore nominale ±20% | Frequenza operativa f: valore nominale ±20% | — |

| Intervallo di temperatura di esercizio (TA): -55 ℃ ~ 125 ℃ | Nota: * indica che può essere personalizzato secondo le esigenze dell'utente. | Tabella 2 Caratteristiche elettriche | Parametro |

| Condizioni | — | Serie HSDC14569 | (VSu003d15V, VLu003d+5V) |

| Standard militare (Q/HW20725-2006) | — | 2V | min. |

| Massimo | — | Risoluzione | Codice digitale parallelo di sistema binario |

| 16 bit | — | 2V | Precisione |

| ± 10% della tensione del segnale, tensione di riferimento e intervallo di oscillazione della frequenza di esercizio | — | -2 minuti angolari | +2 minuti angolari |

| Intervallo di frequenza di riferimento | — | 50 Hz | 2600 Hz |

| Intervallo di tensione di riferimento | — | 115V | Impedenza di ingresso di riferimento |

4,4 kΩ 4,4 kΩ | — | 0 | 129,2 kΩ |

Intervallo di tensione del segnale Intervallo di tensione del segnale | — | 0 | 90V |

Impedenza di ingresso del segnale Impedenza di ingresso del segnale | — | 0 | 4,4 kΩ |

| 102,2 kΩ | — | Sfasamento segnale/riferimento | —70° |

| +70° | — | Livello logico di input | Logica "1" ≥3,3 V |

| Logica "0" ≤0,8 V | — | ingresso | 0,8 V |

| ingresso | — | 0,8 V | |

| ingresso | — | — | 0,8 V |

| Livello di output logico | — | — | Logica "1" ≥3,3 V |

| Logica "0" ≤0,8 V | — | — | Uscita digitale del codice angolare |

| Logica "1" ≥3,3 V | — | — | Logica "0" ≤0,8 V |

| Conversione dell'uscita del segnale di occupato (CB). | — | 200 ns | 600 ns |

| Uscita bit di rilevamento errori | La logica "0" indica l'errore | — | Capacità di carico |

| 3TTL | Velocità di tracciamento | ||

| 2,5 rps | Accelerazione costante | ||

| +10V Attuale VSu003d+15V 10 mA |  VS u003d—15V |

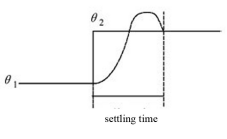

velocità. Il processo di oscillazione dell'angolo digitale di uscita è mostrato in

velocità. Il processo di oscillazione dell'angolo digitale di uscita è mostrato in 6. Principio di funzionamento (Fig. 3)

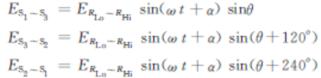

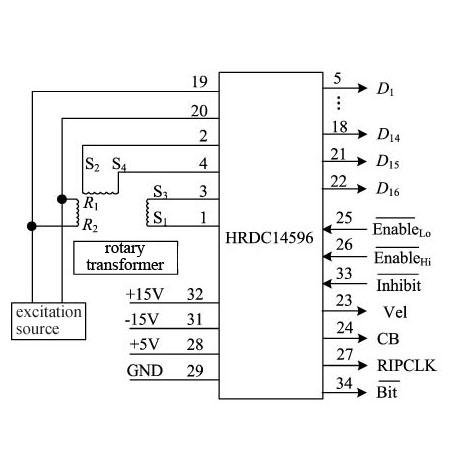

6. Principio di funzionamento (Fig. 3)| Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1459) Il segnale di ingresso di synchro (o resolver) viene convertito nel segnale ortogonale attraverso l'isolamento differenziale interno: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofDove, θ è l'angolo di ingresso analogico. Fig.2 Curva di risposta al passo | Questi due segnali e l'angolo digitale φ del contatore interno reversibileof sono moltiplicati nel moltiplicatore delle funzioni Seno e Coseno e sono errore trattato: |

| amplificazione, discriminazione di fase e filtrazione di integrazione, se | θ-φ≠0, l'oscillatore controllato in tensione emetterà gli impulsi e il | il contatore reversibile conta, fino a quando θ-φ diventa zero entro la precisione di | il convertitore, durante questo processo, la conversione tiene traccia del cambio di | inserire sempre l'angolo. | Metodo di lettura: |

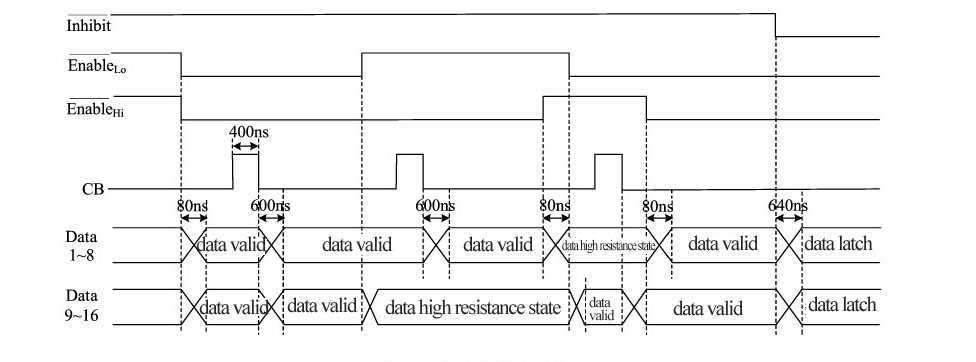

| 1 | S1 | Sono disponibili due metodi per il trasferimento dei dati: | 25 |  | (1) Metodo di inibizione: |

| 2 | S2 | Dopo 640 ns | 26 |  | logico basso, i dati di uscita sono validi e il convertitore realizza il trasferimento dei dati |

| 3 | S3 | e | 27 | . Dopo il rilascio di Inhibit, il sistema genererà automaticamente un impulso con ampiezza pari all'impulso di occupato per l'aggiornamento dei dati. | (2) Modalità busto: |

| 4 | S4 | Al bordo di crescente dell'impulso occupato, conta i tre stati reversibili; sul bordo discendente dell'impulso Occupato, genera internamente un impulso di latch di ampiezza pari all'impulso di Occupato per l'aggiornamento dei dati del latch a tre stati, la sequenza temporale del trasferimento dei dati è mostrata in Fig.4, in altre parole, dopo 600 ns della logica di occupato basso, il trasferimento stabile dei dati è valido. Nella modalità di lettura asincrona, l'uscita Occupato è un treno di impulsi di livello CMOS. La larghezza del suo livello alto e basso dipende dalla frequenza operativa e dalla velocità di rotazione del dispositivo selezionato. | 28 | VL | Fig.4 Sequenza temporale del trasferimento dei dati |

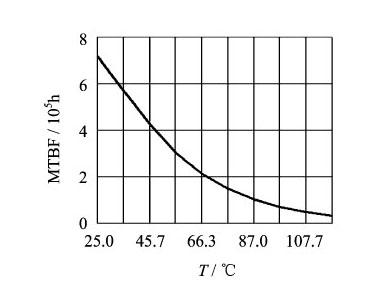

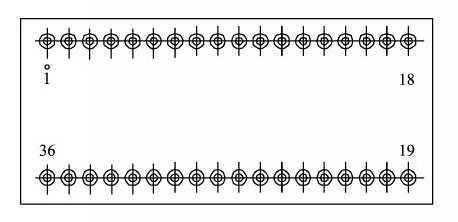

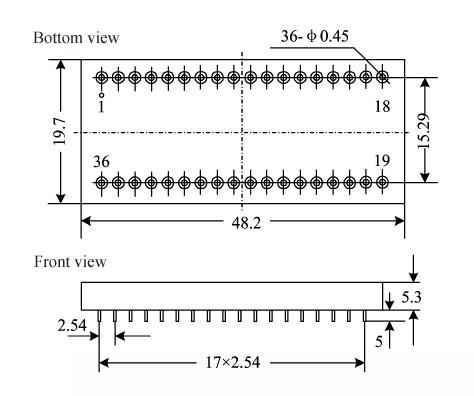

| 7. Curva MTBF (Fig.5) | Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1459) | Fig.5 Curva della temperatura MTBF | 29 | 8. Designazione del pin (Fig.6, Tabella 3) | Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1459) |

| 19 | Fig.6 Denominazione pin (vista dal basso) | (Nota: secondo GJB/Z299B-98, buone condizioni del terreno previste) | 30 | NC | Tabella 3 Denominazione del pin |

| 20 | RL | Spillo | 31 | Simbolo | Significato |

| 21 | Spillo | Simbolo | 32 | VS | Significato |

| 22 | Ingresso resolver S1 (o ingresso sincro S1) | Controllo digitale abilitato degli 8 bit inferiori | 33 | Ingresso resolver S2 (o ingresso sincrono S2) | Controllo digitale abilitato di 8 bit superiori |

| 23 | Ingresso resolver S3 (o ingresso sincrono S3) | RIPCLK | 34 | Uscita del segnale a zero bit | Ingresso resolver S4 (lasciare non connesso) |

| 24 | CB | +5V di alimentazione | 5月18日 | NC | D1-D14 |

| Uscita digitale 1(MSB)-14 | GND |

| Terra | RH Ciao |

| Ingresso del segnale di riferimento di fascia alta | Nessuna connessione |

| RL | Ingresso del segnale di riferimento di fascia bassa |

-VS

-VS -15V alimentazione

-15V alimentazione

D15 Uscita digitale 15

Uscita digitale 15 ).

).

+15V alimentazione

D16

Uscita digitale 16 (LSB)

Inibire

Ingresso segnale statico

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Ingresso del segnale di riferimento di fascia bassaofMinore | Ingresso del segnale abilitato per cifre a 8 bit, questo pin è il pin di ingresso logico diofcontrollo del gating dei dati, la sua funzione è di eseguire il controllo a tre stati |

|  |

| esternamente sui dati di uscita a 8 bit inferiori del convertitore. Il livello basso è | valido, i dati di uscita a 8 bit inferiori del convertitore occupano i dati |

stato di resistenza e il dispositivo non occupa il bus dati. Abilitaree il tempo di ritardo di rilascio è di 600 ns (max). | più alto | Ingresso del segnale abilitato per cifre a 8 bit, questo pin è il pin di ingresso logico di | controllo del gating dei dati, la sua funzione è di eseguire il controllo a tre stati | esternamente sui dati di uscita a 8 bit superiori del convertitore. Basso livello | è valido, i dati di uscita a 8 bit più alti del convertitore occupano ilbus di dati; A livello alto, il pin dei dati di output a 8 bit superiori è in alto | stato di resistenza e il dispositivo non occupa il bus dati. Abilitare | e il tempo di ritardo di rilascio è di 600 ns (max). | Inibire statico |

segnale di ingresso, questo pin è il pin di ingresso della logica di controllo, la sua funzione | è quello di emettere dati esternamente al convertitore per realizzare optional | Nicontrollo di blocco o bypass. Ad alto livello, i dati di output del | il convertitore esce direttamente senza latching; a basso livello, l'uscita | i dati del convertitore sono bloccati, i dati non vengono aggiornati, ma ilil loop interno non viene interrotto e il tracciamento sta funzionando per tutto il tempo | tempo, Inhibit ha collegato la resistenza di pull-up internamente. Dopo 600 ns (max) ritardo di | Au fronte discendente del segnale statico, i dati diventano stabili (se il | il dispositivo occupa il bus dati, ovvero quando emette i dati dipendesullo stato di | eUscita segnale CB “Occupato”, questo segnale indica se il codice binario |

X

X