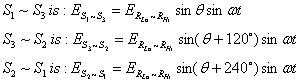

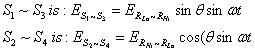

La potenza operativa adotta ± 15 V e + 5 V CC. Esistono due tipi di segnale di uscita: sincro a tre linee e segnale di riferimento (convertitore SDC) o resolver a quattro linee e segnale di riferimento (convertitore RDC); l'uscita adotta codici digitali paralleli del sistema binario.

| Risoluzione: 12 bit, 14 bit |  |

| Alta velocità di tracciamento | |

| Integrazione ibrida, custodia in metallo | |

| Uscita latch a tre stati | |

| Con uscita del segnale di velocità Vel | |

| Compatibilità indefinita con la serie AD1740 |

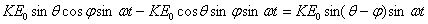

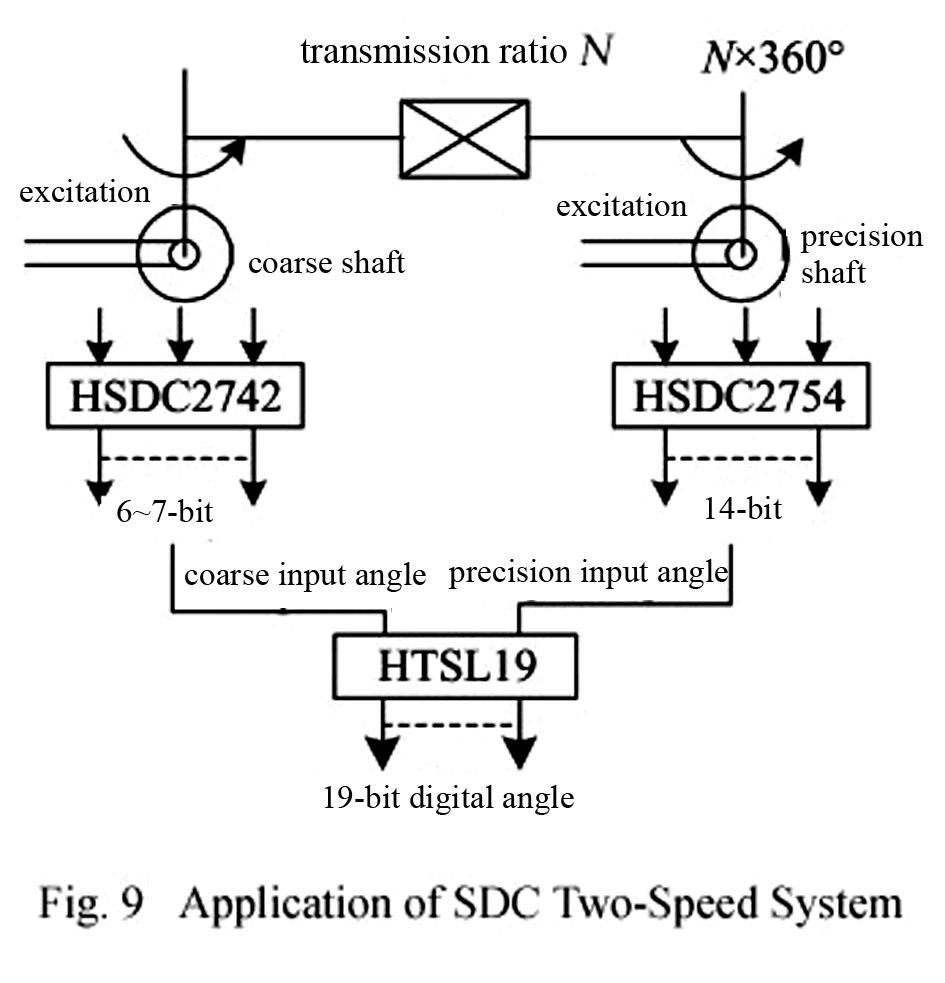

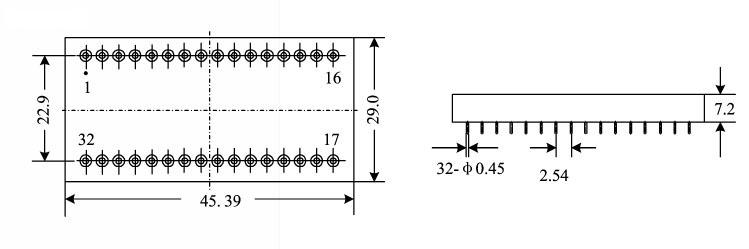

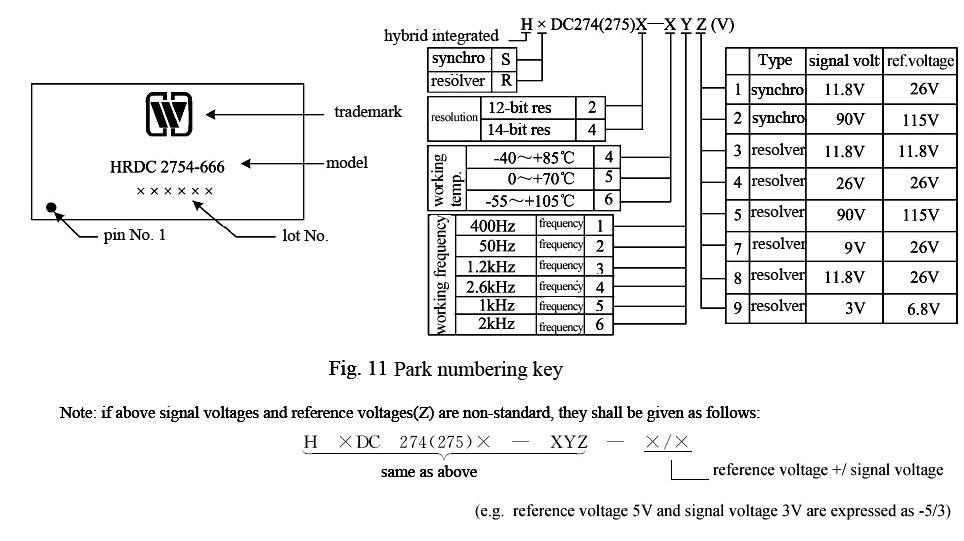

La serie HSDC/HRDC27 è il convertitore da digitale a synchro o da resolver a convertitori digitali per il tracciamento continuo di servo loop di tipo II, si aggancia ed emette parallelamente dati codificati binari naturali a 12 o 14 bit con metallo dual-in-line a 32 linee pacchetto, presenta i vantaggi di volume ridotto, peso leggero e alta affidabilità ecc., È ampiamente applicato in un sistema di controllo automatico come sistema radar, sistema di navigazione, ecc.

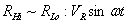

La potenza operativa adotta ± 15 V e + 5 V CC. Esistono due tipi di segnale di uscita: sincro a tre linee e segnale di riferimento (convertitore SDC) o resolver a quattro linee e segnale di riferimento (convertitore RDC); l'uscita adotta codici digitali paralleli del sistema binario.

Tabella 2 Condizioni classificate e condizioni operative consigliate

Assoluto max. valore valutato | Tensione di alimentazione Vs: ± 17,5 V |

Tensione logica VL: +5,5 V | |

Intervallo di temperatura di conservazione: -55 ℃ ~ + 125 ℃ | |

Condizioni Operative Raccomandate | Tensione di alimentazione Vs: ± 5 V |

Tensione logica VL: 5 V | |

Valore effettivo della tensione di riferimento VRef: ±10% del valore nominale | |

Validità della tensione del segnale V1*: ±5% del valore nominale | |

Frequenza di riferimento f*: 50 Hz~2,6 kHz | |

Intervallo di temperatura di esercizio TA: -40~+85℃,-55~+105℃ |

Nota: * indica che può essere personalizzato secondo requisito dell'utente.

| produzione; leggere dati a 12 o 14 bit; impostare Inhibit su "1" logico in modo da |  |

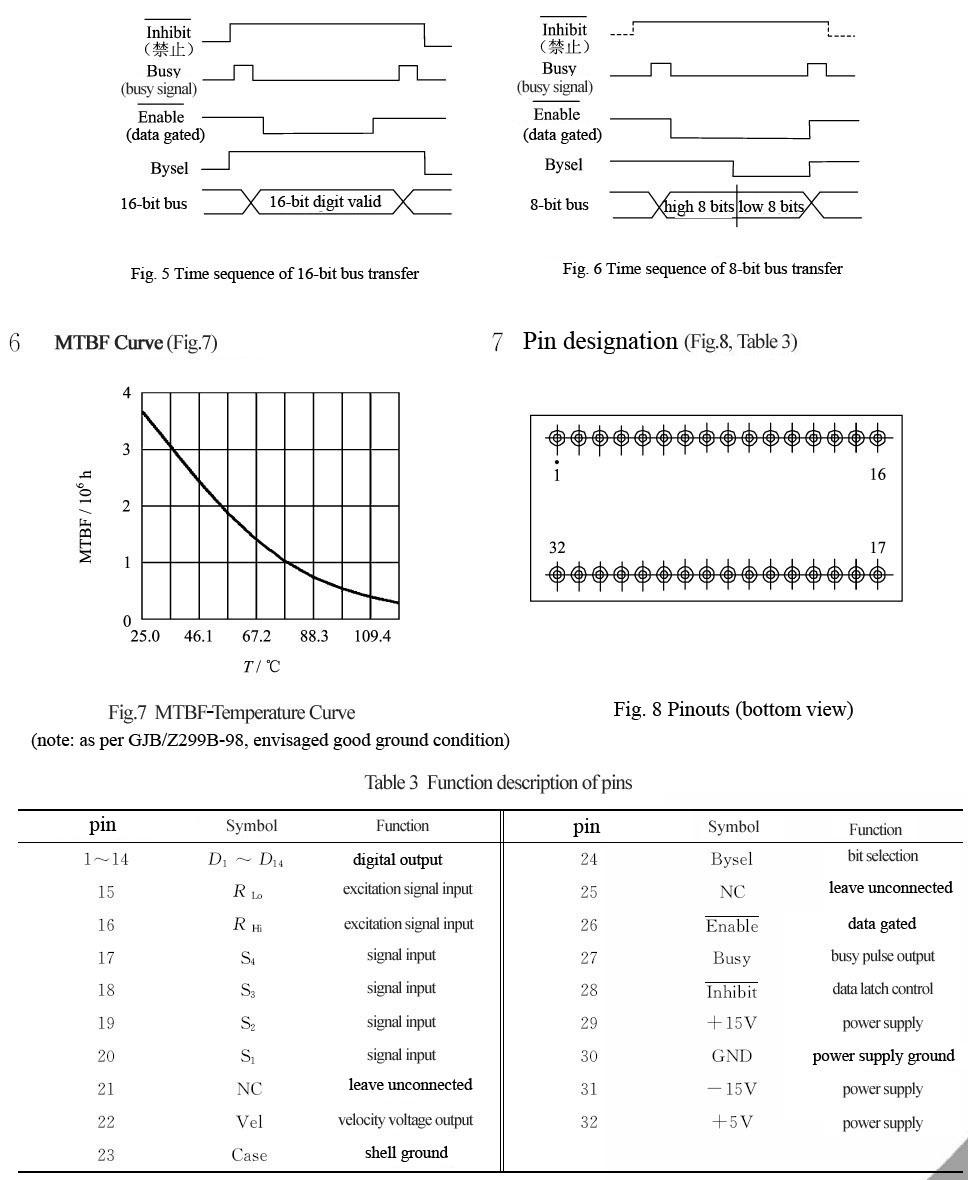

| trasferimento a 16 bit). | B: il convertitore è collegato al bus a 8 bit, i bit D1~D8 sono collegati al bus dati e il resto è vuoto. |

| |

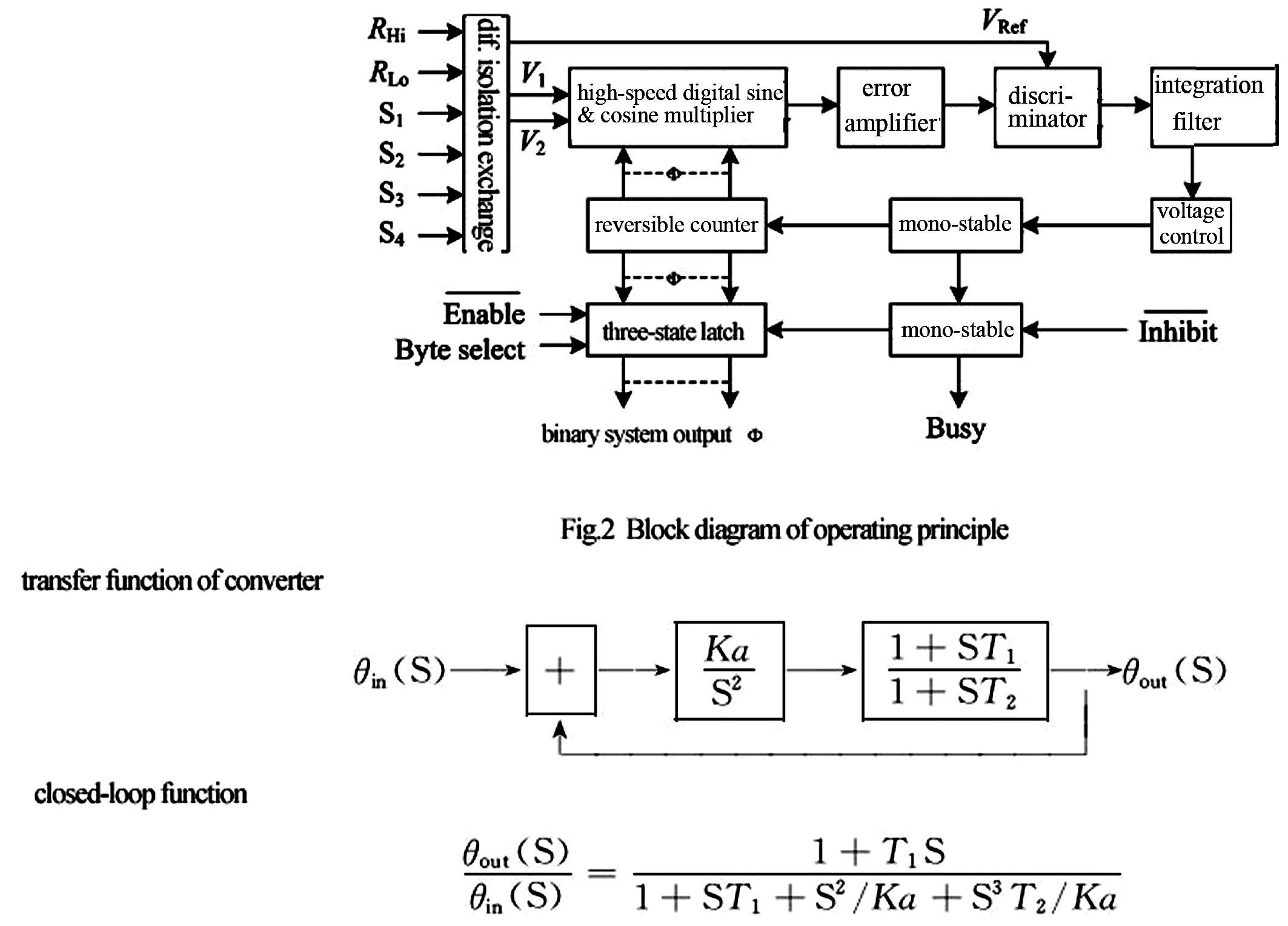

| Inibire è | |

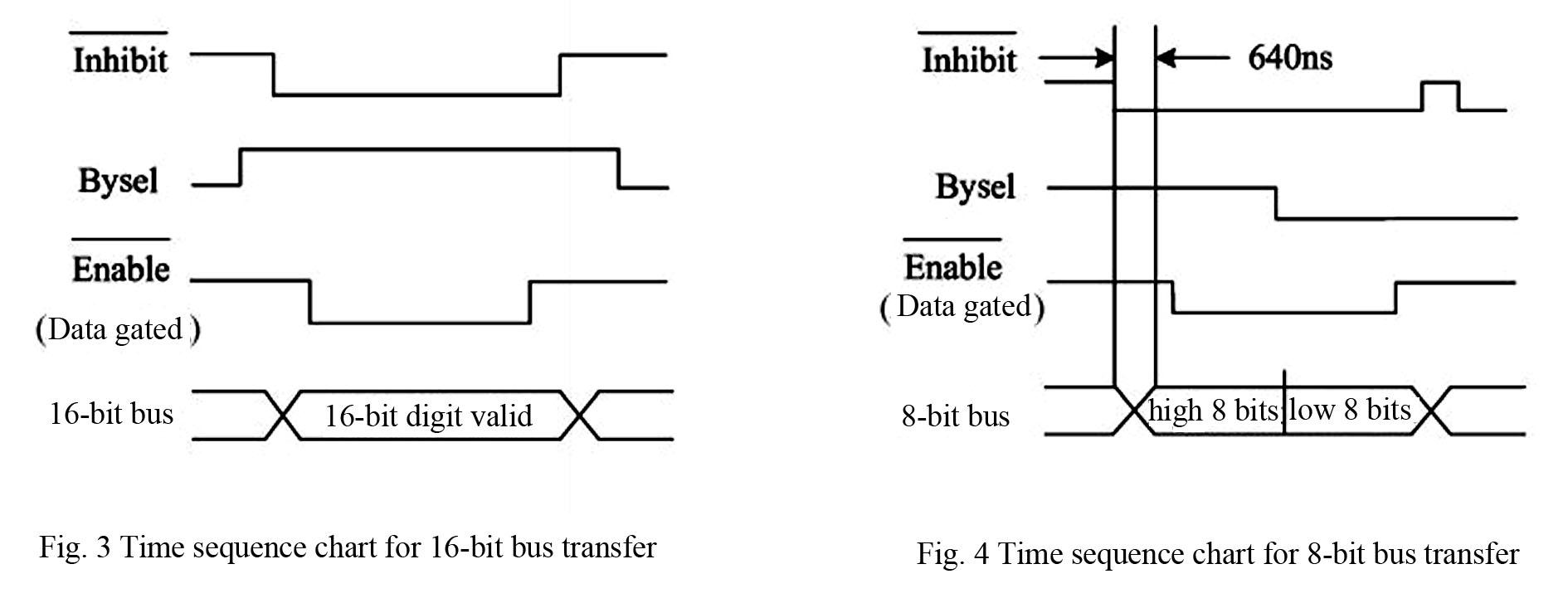

| Abilitare a "0" logico, i dati di latch all'interno del convertitore sono consentiti | essere emesso; se Byse1 è impostato a “1” logico, il convertitore legge direttamente | i dati superiori a 8 bit, se Byse1 è impostato a “0” logico, il convertitore legge | i restanti bit, aggiunge automaticamente zero per i bit incompleti; impostare il controllo di blocco dei dati di inibizione (segnale di inibizione) su "1" logico per prepararsi alla lettura dei successivi dati validi (vedere la Fig. 3 e la Fig. 4 per la sequenza temporale di trasferimento a 8 bit) | (2) Metodo occupato (lettura asincrona): | In modalità di lettura asincrona, Inibisci il controllo del blocco dei dati (segnale di inibizione) è impostato su "1" logico o vuoto, indipendentemente dal fatto che il circuito interno sia sempre in | deve essere determinato lo stato stabile o se i dati di uscita sono validi | attraverso lo stato di segnale occupato Occupato. Quando il segnale di occupato è alto | livello, indica che i dati vengono convertiti e i dati a questo |

| il tempo è instabile e non valido; quando il segnale di occupato è a basso livello, esso | indica che la conversione dei dati è stata completata e i dati a questo punto | Au | il tempo è stabile e valido. Quando si verifica un livello alto in Occupato durante la lettura, | Au | la lettura di questo tempo non è valida. In modalità di lettura asincrona, Occupato | Au | l'uscita è un treno di impulsi di livello TTL, la larghezza tra è correlata a | velocità di rotazione. Allo stesso modo, ci sono anche 8 bit e 16 bit a due usi |

X

X