| Alta precisione |  |

| Taglia piccola | |

| Alta velocità di tracciamento | |

| Tracciamento ininterrotto durante il trasferimento dei dati | |

| Uscita latch a tre stati | |

| Basso consumo energetico |

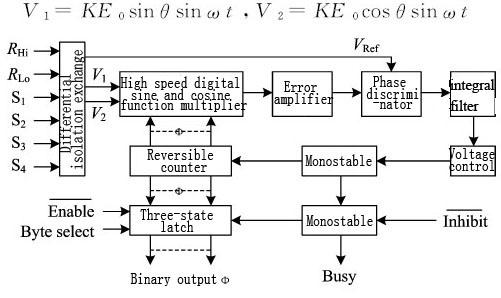

il segnale di uscita è un codice binario naturale parallelo bufferizzato | latch a tre stati e compatibile con il livello TTL. |

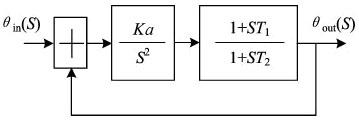

Il prodotto applica un servocircuito di secondo ordine con dimensioni e luce ridotte | |

peso, e l'utente può usarlo in modo molto conveniente controllando | |

pin di segnale. | |

Tabella 2 Condizioni nominali e condizioni operative consigliate | Massimo valore di valutazione assoluto |

Tensione di alimentazione +VS: 12,5 ~ 17,5 V | |

Tensione di alimentazione -VS: -17,5~-12,5V | |

Tensione logica VL: 7V | |

Intervallo di temperatura di conservazione: -40 ~ + 100 ℃ | |

Condizioni Operative Raccomandate |

Tensione di riferimento (valore efficace) VRef: valore nominale ±10% | Tensione del segnale (valore effettivo) V1*: valore nominale ±10% Frequenza di riferimento f*: valore nominale ±10% | Intervallo di temperatura di esercizio TA: -40~+85℃ | Nota: * indica che può essere personalizzato secondo le esigenze dell'utente. | |

Tabella 2 Caratteristiche elettriche | Parametro | |||

Condizioni (-40~+85℃) | (Se non diversamente specificato) | 12 | 16 | (serie MSDC/MRDC37) |

Unità | – | 3 | 36 | min. |

Massimo | Risoluzione/RES | Intervallo di 0~360º | – | V |

Po | Velocità di tracciamento/St① | – | rps | V |

Alto livello di uscita/VOH | ATu003d25℃ | – | 2.4 | W |

Livello di uscita basso/VOL | ATu003d25℃ | – | 0.8 | % |

Consumo di energia/PD | – | 2 | ATu003d25℃ | V |

1.3 | – | 2 | 90 | V |

Vel linearità/ERl | – | 30 | ATu003d25℃ | Hz |

1.0 | – | ±3 | Intervallo di tensione di riferimento | 115 |

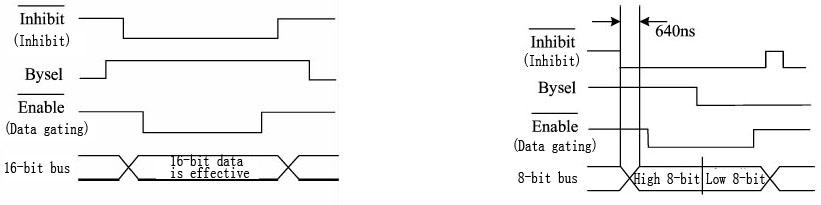

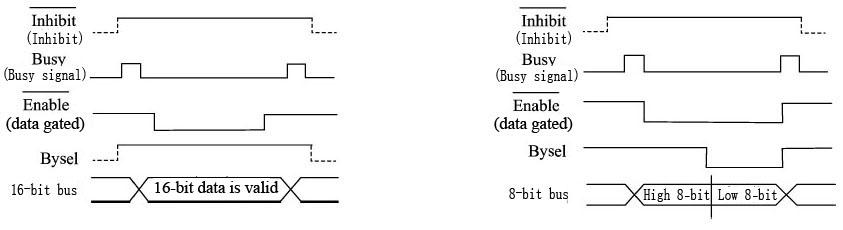

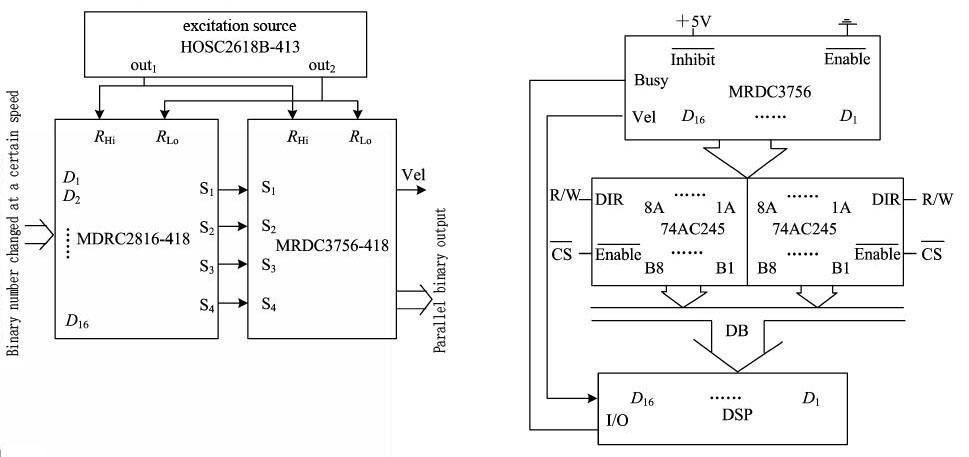

B: il convertitore è collegato al bus a 8 bit, i bit D1~D8 sono collegati al bus dati e il resto è vuoto. | Imposta Inhibit da 1 logico a 0 logico (blocco dati) e attendi 1μs; impostare Enable su 0 logico per consentire al latch nel convertitore di emettere dati; impostare | Bysel su 1 logico, leggi direttamente i dati a 8 bit alti, imposta Bysel su | 0 logico, legge i dati in altri bit con riempimento automatico dello zero | i bit liberi; impostato su 1 logico per prepararsi alla lettura dei successivi dati effettivi (Fig. 5). | Inibire | Fig4 Sequenza temporale del trasferimento bus a 16 bit Fig5 Sequenza temporale del trasferimento bus a 8 bit | (2) Metodo occupato (lettura asincrona): | In modalità di lettura asincrona, è impostato Inhibit su 1 logico o vuoto, indipendentemente dal fatto che il loop interno sia sempre nel |

1 | D1 | deve essere determinato lo stato stabile o se i dati di uscita sono validi | 13 | attraverso lo stato del segnale di occupato Occupato. Quando il segnale di occupato è alto | livello, indica che i dati sono in corso di conversione e i dati a questo | 25 | il tempo è instabile e non valido; quando il segnale di occupato è a basso livello, esso | indica che la conversione dei dati è stata completata e i dati a questo punto |

2 | D2 | il tempo è stabile e valido. Quando si verifica un livello alto in Occupato durante la lettura, | 14 | la lettura in questo momento non è valida. In modalità di lettura asincrona, il | L'uscita occupata è un treno di impulsi di livello TTL, la sua larghezza dipende da esso | 26 | velocità di rotazione, ci sono anche due metodi di utilizzo del bus, ovvero 8 bit | e 16 bit, anche la lettura dei dati durante l'effettiva uscita dei dati |

3 | D3 | controllato da Enable , fare riferimento al diagramma della sequenza temporale per il trasferimento dei dati (Fig. 6 e Fig. 7). | 15 | Fig.6 Diagramma sequenza temporale per trasferimento bus a 16 bit Fig.7 Diagramma sequenza temporale per trasferimento bus a 8 bit | Pin del segnale di stato: Occupato, DIR, R, C. | 27 | Quando l'ingresso del convertitore cambia, Busy emette un treno di impulsi | di livello CMOS, la sua frequenza è determinata dalla rotazione più alta |

4 | D4 | velocità. Quando Occupato è ad alto livello, significa il servo del secondo ordine | 16 | circuito nel convertitore è in funzione, i dati all'estremità dell'uscita digitale sono | mutevole; al contrario, il computer può leggere direttamente i dati. | 28 | Il segnale DIR viene utilizzato per indicare la rotazione avanti/indietro. Quando l'uscita | |

5 | D5 | il codice è in aumento, l'output è di alto livello; quando il codice di output è | 17 | NC | conto alla rovescia, l'uscita è di basso livello. | 29 | Uscita segnale zero R.C: quando i dati di uscita passano da tutti 1 a | tutto 0 o i dati di output decrescono da tutto 0 a tutto 1, il |

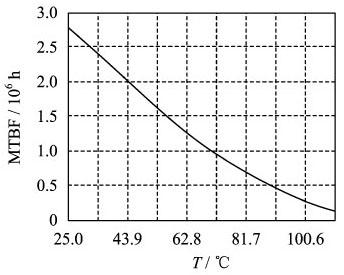

6 | D6 | l'uscita è un impulso positivo, la larghezza dell'impulso è 200μs. | 18 | 5. Curva MTBF di convertitori da sincro a digitale o da resolver a convertitori digitali (serie MSDC/MRDC37)(Fig. 7) | Fig. 8 Curva della temperatura MTBF | 30 | (Nota: secondo GJB/Z299B-98, buone condizioni del terreno previste) | |

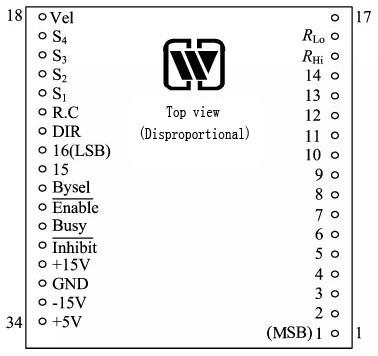

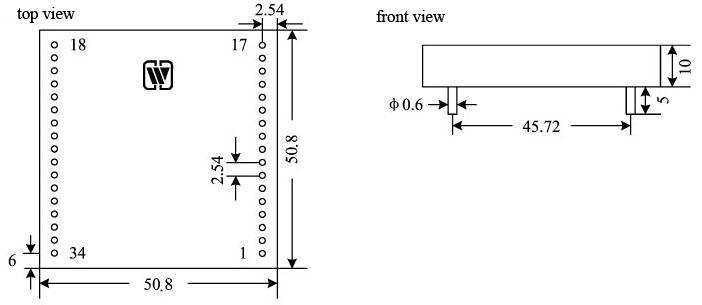

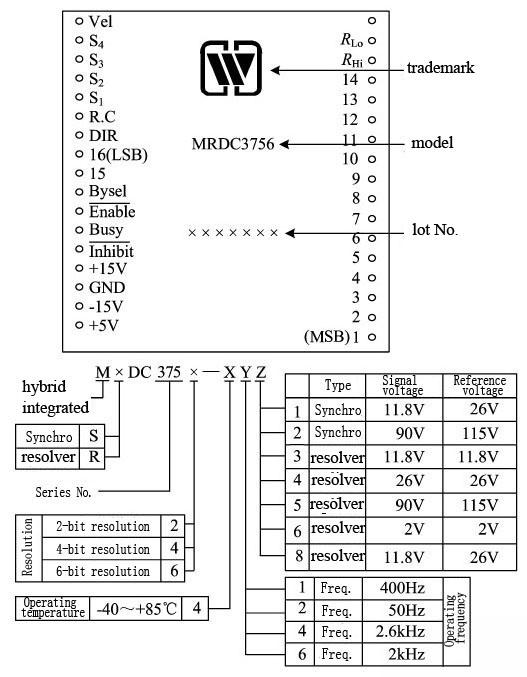

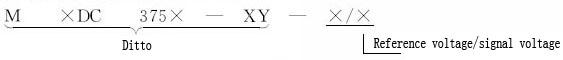

7 | D7 | 6. Designazione dei pin dei convertitori da sincro a digitale o da resolver a convertitori digitali (serie MSDC/MRDC37)(Fig. 9, Tabella 3) | 19 | S4 | Fig.9 Denominazione del pin (vista dall'alto) | 31 | Tabella 3 Denominazione del pin | Spillo |

8 | D8 | Simbolo | 20 | S3 | Significato | 32 | Spillo | Simbolo |

9 | D9 | Significato | 21 | S2 | Spillo | 33 | Simbolo | Significato |

10 | Uscita digitale 1 (bit più alto) | D13 | 22 | S1 | Uscita digitale 13 | 34 | VL | D16 |

11 | Uscita digitale 16 | Uscita digitale 2 | 23 | D14 | Uscita digitale 14 | |||

12 | D15 | Uscita digitale 15 | 24 | Uscita digitale 3 | RH Ciao |

Ingresso segnale di riferimento (fascia bassa) | Abilita segnale | Uscita digitale 5 | Senza uscita | Impegnato | Segnale di occupato |

Uscita digitale 6 | Vel | 7 | Uscita tensione di velocità | 13 | Segnale di inibizione |

2 | Uscita digitale 7 | 8 | Ingresso del segnale | 14 | +Vs |

3 | Alimentazione +15V | 9 | Uscita digitale 8 | 15 | Ingresso del segnale |

4 | GND | 10 | Terra di alimentazione | 16 | Uscita digitale 9 |

5 | Ingresso del segnale | 11 | -Vs | ||

6 | -Alimentazione 15V | 12 | D10 |

| |

| Ingresso del segnale | Alimentazione +5V |

X

X