| Sistema completo a 2 velocità |  |

| Rapporti di velocità programmabili nel canale grosso/fine | |

| 1:8, 1:16, 1:32, 1:64 | |

| Uscita digitale con latch a 3 stati | |

| La risoluzione massima è di 20 bit | |

| La precisione massima è di 5 Arcsec |

| contengono convertitori o resolver bidirezionali grossolani/fini a |

|

| convertitori digitali e circuito logico di correzione degli errori richiesto da due |

I rapporti di velocità della combinazione grossolana/fine dei prodotti della serie HTS20 sono | 1:8, 1:16, 1:32, 1:64, il rapporto di velocità richiesto può essere ottenuto da | programma esterno. È comodo da usare. Input grossolano/fine a due vie i segnali sono segnali di synchro a tre fili o resolver a quattro fili. Uscita convertitore SDC/RDC a 2 velocità programmabile serie HTS20 naturale | codici binari paralleli. Il massimo è fino a 20 bit. Hanno 3 stati | chiavistelli. | |

4 SPECIFICHE TECNICHE dei Convertitori Sincro a Digitale o | Resolver a convertitori digitali serie HTS20 SDC/RDC programmabili a 2 velocità | ||||

Convertitori ( Tab 2, Tab 3 ) | Tabella 2 Condizioni nominali e condizioni operative consigliate * significa che può essere fatto su ordinazione. Tabella 3 Caratteristiche elettriche Caratteristiche Condizioni | - - - - | 17 18 19 20 | HTS20R/HTS20S | |

Standard militare d'affari | (Q/HW30925-2006) Unità Commenti min Massimo | - - - - | 40 20 10 5 | Risoluzione | |

(opzionalmente controllato da SC1, SC2) rapporto di velocità 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 po 90 | Precisione (0°~360°) Hz V V | |

|  |

10k 115 | |

,

, Resolver a convertitori digitali serie HTS20 SDC/RDC programmabili a 2 velocità

Resolver a convertitori digitali serie HTS20 SDC/RDC programmabili a 2 velocità Convertitori ( Fig 2, Fig 3 )

Convertitori ( Fig 2, Fig 3 ) ,

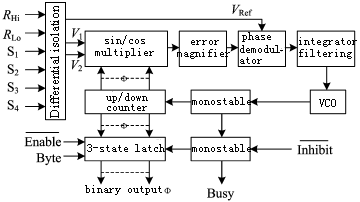

, (1) Convertitore a velocità singola

(1) Convertitore a velocità singola I principi di funzionamento del convertitore a velocità singola sono mostrati in fig2., i principi sono riassunti come segue:

I principi di funzionamento del convertitore a velocità singola sono mostrati in fig2., i principi sono riassunti come segue: Dove θ è l'angolo di ingresso analogico.

Dove θ è l'angolo di ingresso analogico. ,

, I due segnali vengono moltiplicati per l'angolo digitale φ dell'alto/basso interno

I due segnali vengono moltiplicati per l'angolo digitale φ dell'alto/basso interno .

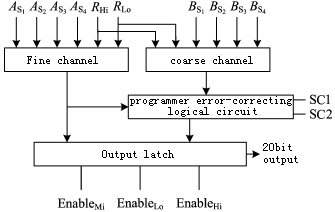

.I principi di funzionamento del convertitore a 2 velocità sono mostrati in fig3. Il | il funzionamento del canale grosso e fine del convertitore a 2 velocità è il |

|  |

| come sopra menzionato a velocità singola, ma è composto da un convertitore a 2 velocità due set di convertitore a velocità singola e logica di errore del programmatore circuito. Il canale grossolano soddisfa la conversione da un angolo logico di 10 ~ 12 bit | |

angolo ad angolo digitale. angoli digitali convertiti da canale grossolano e | I canali fini vengono inseriti nella logica di correzione degli errori del programmatore | rispettivamente del circuito. Dopo l'elaborazione e la correzione dell'errore, lo farà | emette una cifra binaria parallela a 20 bit, che viene immessa in uscita | latch e bufferizzato per emettere l'angolo digitale, soddisfacendo l'intero | conversione. | |

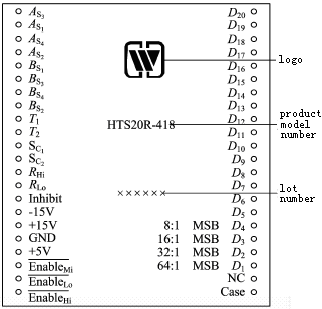

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Figura2 Schema a blocchi funzionale Figura3 Schema a blocchi funzionale di convertitore a velocità singola di convertitore a 2 velocità (3) Modalità e tempi di trasferimento dei dati Le uscite dei convertitori a 2 velocità della serie HTS20 raggiungono i 20bit. Attraverso e che prendono il controllo a 3 stati del latch di uscita, il convertitore a 2 velocità può essere facilmente collegato al bus dati. e T1 T2 sono tutti validi a basso livello. EnableLo controlla gli 8 bit bassi, EnableMi controlla gli 8 bit intermedi, i controlli EnableHi restano i bit alti. I dati dei convertitori a 2 velocità serie HTS20 si leggono come segue: Impostare allo "0" logico, dopo 490μm, i dati in latch a 3 stati del convertitore sono aggiornato. Può leggere dati di 8 bit bassi, 8 bit medi e bit alti attraverso il controllo e Figura 4 Fornisce i tempi di lettura dei dati quando sono collegati un convertitore a 2 velocità e un bus dati a 8 bit. Per garantire una conversione ad alta precisione del convertitore a 2 velocità, prestare attenzione a quanto segue:

| Le ampiezze dei segnali di ingresso dei canali grossolani e fini devono essere garantite entro il valore nominale del 10%. Le frequenze dei segnali di ingresso e dei segnali di riferimento dei canali grossolani e fini devono corrispondere alle frequenze operative specificate. Sfasamento tra segnale di ingresso e segnale di riferimento di grossolano canale e fase tra il segnale di ingresso e il segnale di riferimento di fine il canale deve essere inferiore a 10°. La distorsione delle onde dei segnali di ingresso e dei segnali di riferimento dei canali grossolani e fini deve essere inferiore al 5%. La variazione di alimentazione di +5V, ±15V dovrebbe essere garantita entro ±5%. 6 DIAGRAMMA MTBF dei Convertitori Sincro a Digitali o Resolver a convertitori digitali serie HTS20 SDC/RDC programmabili a 2 velocità Convertitori ( Fig 5 ) 7 CONFIGURAZIONI PIN di Synchro to Digital Converter o Resolver a convertitori digitali serie HTS20 SDC/RDC programmabili a 2 velocità Convertitori ( Fig6, Tab4 ) Figura 5 MTBF rispetto alla temperatura Figura 6 Vista dall'alto dei piedini (Nota: secondo GJB/Z 299B-98, supponendo quel terreno è in buone condizioni) Tabella 4 Descrizione del pin Spillo Mnemonico Descrizione Spillo Mnemonico Descrizione As3 As1 As4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | As2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RH Ciao RLo Inibire -15V +15V GND +5V Ingresso canale fine Ingresso canale fine | Ingresso canale fine Ingresso canale fine Ingresso canale grossolano Ingresso canale grossolano Ingresso canale grossolano Ingresso canale grossolano Perno di regolazione per sfasamento tra segnale e riferimento Perno di regolazione per sfasamento tra segnale e riferimento Perno di controllo del programma per grossolano e rapporti di velocità fini Perno di controllo del programma per grossolano e rapporti di velocità fini Pin di ingresso per riferimento alto Pin di ingresso per riferimento basso Segnale di inibizione Ingresso -15V Ingresso +15V terra Ingresso +5V abilita i dati a 8 bit centrali | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

Non collegato Uscita dell'angolo digitale combinato più alto | Uscita dell'angolo digitale combinato | Uscita dell'angolo digitale combinato Uscita dell'angolo digitale combinato | Uscita dell'angolo digitale combinato | Uscita dell'angolo digitale combinato Uscita dell'angolo digitale combinato | Uscita dell'angolo digitale combinato |

Uscita dell'angolo digitale combinato | Uscita dell'angolo digitale combinato | 8 | Uscita dell'angolo digitale combinato | 15 | Uscita dell'angolo digitale combinato |

2 | Uscita dell'angolo digitale combinato | 9 | Uscita dell'angolo digitale combinato | 16 | Uscita dell'angolo digitale combinato |

3 | Uscita dell'angolo digitale combinato | 10 | Uscita dell'angolo digitale combinato | 17 | Uscita dell'angolo digitale combinato |

4 | Uscita dell'angolo digitale combinato | 11 | Emissione dell'angolo digitale meno combinato | 18 | Nota: |

5 | I pin 3,7 di HTS20S non sono collegati. | 12 | As1, As2, As3, As4 sono ingressi di canale fini. Se synchro è dotato di tre fili, As4 non viene utilizzato. | 19 | Bs1, Bs2, Bs3, Bs4 sono ingressi di canale grossolani. Se synchro è dotato di tre fili, Bs4 non viene utilizzato. |

6 | RHi, RLo sono l'ingresso del segnale di riferimento. | 13 | L'inibizione è il segnale di inibizione che è collegato all'alimentazione a 5 V tramite un resistore di pull-up. Quando Inhibit è logico “0”, inside è inibito. Dopo 490 ns, i dati validi vengono emessi e possono essere letti. Quando è logico "1", il convertitore ripristina lo stato di tracciamento, i dati emessi sono dati non validi. | 20 | Inibire |

7 | e | 14 | sono tre pin di controllo dello stato dell'output dei dati, che determinano lo stato |

Il caso è il perno del caso.

D1~D20 sono le uscite dell'angolo digitale combinato. D20 è meno significativo

po. Quando il rapporto di velocità è 1:8, D4 è il bit più significativo. Quando la velocità | il rapporto è 1:16, D3 è il bit più significativo. Quando il rapporto di velocità è 1:32, D2 | è il bit più significativo. Quando il rapporto di velocità è 1:64, D1 è il massimo | bit significativo. TABELLA DEI PESI A 8 BIT di Convertitori Sincro a Digitali o Resolver | a convertitori digitali serie HTS20 SDC o RDC programmabili a 2 velocità Convertitori ( Tab 5 ) | Tabella 5 Tabella dei pesi dei bit | Po | numero Peso (gradi) | Po |

numero | Peso (gradi) Po | numero | Peso (gradi) | 1(MSB) | 180.0000 1.1063 | 0,011(40 secondi) | 90.0000 |

|

|

| 45.0000 |

X

X