| Conversione dell'isolamento differenziale interno |  |

| Risoluzione: 16 bit | |

| Uscita latch a tre stati | |

| Tracciamento ininterrotto durante il trasferimento dei dati | |

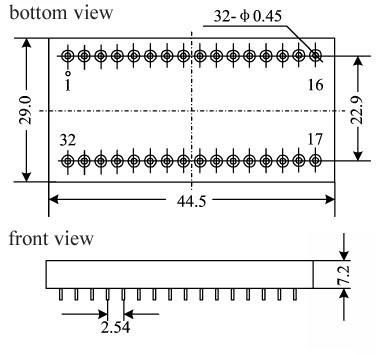

| Pacchetto in metallo a 32 fili |

La serie HSDC/HRDC1746 da synchro/resolver a convertitore digitale è progettata | sul principio di tipo II servo principio di inseguimento e adotta | |||||

ingresso di isolamento differenziale, l'uscita dati adotta il latch a tre stati | modalità, è adatto per la conversione del segnale analogico/segnale digitale di | sincronizzatore a tre fili e resolver a quattro fili. Con alta velocità di conversione | e prestazioni stabili e affidabili, questo dispositivo può essere ampiamente applicato nella misurazione dell'angolo e nel sistema di controllo automatico. | Questo prodotto è realizzato mediante il processo di integrazione ibrida a film spesso ed è | ||

Confezione metallica DIP a 32 fili totalmente sigillata. Sia il design che | ||||||

la fabbricazione del prodotto soddisfa i requisiti di GJB2438A-2002 | “Specifica generale per circuiti integrati ibridi” e specifica | specifiche del prodotto. | ||||

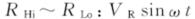

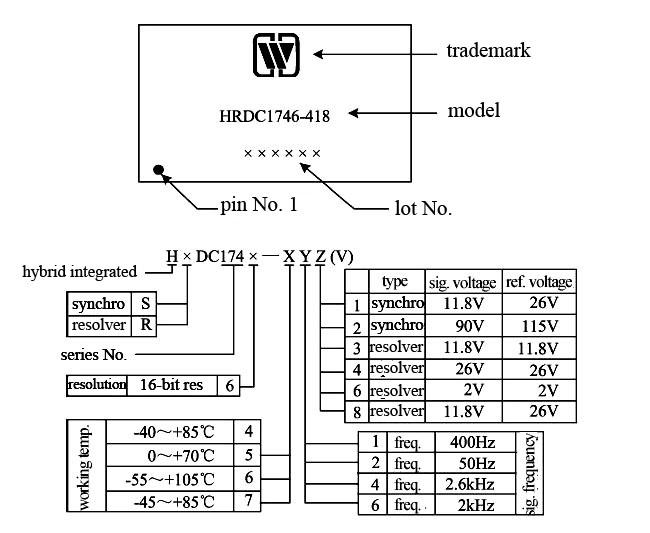

4. Prestazioni elettriche (Tabella 2, Tabella 3) | Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1746) | Tabella 2 Condizioni nominali e condizioni operative consigliate | Tabella 3 Caratteristiche elettriche | Massimo assoluto valore nominale | ||

Tensione di alimentazione Vs: ± 17.25VDC | Parametro | -3 | 3 | |||

HSDC/HRDC | Serie 1746 | 16 | ||||

Appunti | Tensione di alimentazione logica VL: +7V | 50 | Intervallo di temperatura di conservazione: -55 ℃ ~ 150 ℃ | |||

min. | Massimo | 2 | 90 | |||

Condizioni Operative Raccomandate | Tensione di alimentazione Vs: ±15± 5% | 2 | Precisione/minuto angolare | |||

| 2.6k |  |

| Sfasamento tra segnale ed eccitazione:<±10% Tensione del segnale (valore effettivo)/V Intervallo di temperatura di esercizio (TA): -40~+105℃  | |

| Tensione di riferimento (valore effettivo)/V | 115 |

| |

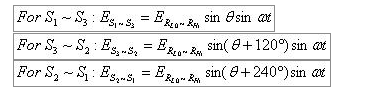

| si ottiene una funzione di errore: |

Attraverso l'amplificazione dell'errore, la discriminazione di fase e la filtrazione di questoof funzione di errore, si ottiene sin(θ-φ), quando θ-φu003d0 (entro la precisione | del convertitore), questo errore renderà la tensione controllataofimpulso di correzione dell'uscita dell'oscillatore per modificare l'angolo digitale binario φ |

| |

| del contatore reversibile in modo da rendere il valore φ dell'uscita uguale al | input θ entro la precisione del convertitore, il sistema diventa stabile |

| e può tenere traccia del cambiamento dell'angolo di input φ. In questo modo, un binario digitale | |

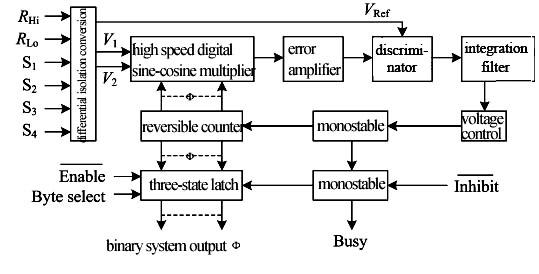

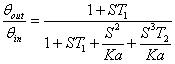

contatore reversibile (Fig. 2). | Fig. 2 Schema a blocchi del circuito | (1) Caratteristiche dinamiche | La funzione di trasferimento del convertitore è mostrata in Fig. 3: | Guadagno ad anello aperto: | Funzione ad anello chiuso: |

1 | NC | Per il modulo di questo modello Kau003d48000/S2, T1u003d7.1ms, T2u003d1.25ms | 17 | NC | Fig. 3 Trasferimento di funzioni del convertitore |

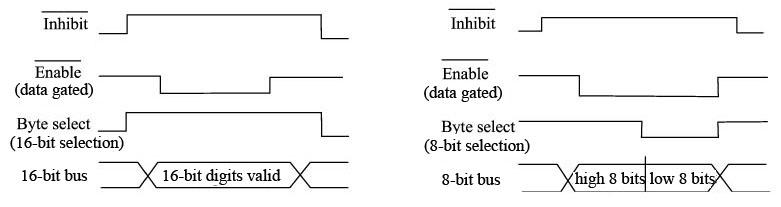

2 | D9 | (2)Metodi di trasferimento dei dati e sequenza temporale | 18 | Controllo selezione chip Abilita | Questo pin è il pin di input della logica di controllo, la sua funzione è quella di output |

3 | dati al convertitore per realizzare il controllo a tre stati. Il livello basso è | valido, i dati di uscita del convertitore occupano il bus dati. Quando è a | 19 | alto livello, il pin di uscita dati del convertitore è in tre stati, il | dispositivo non occupa il bus. |

4 | Selezione byte | Questo pin è il pin di input di controllo, la sua funzione è di eseguire esternamente | 20 | controllo di selezione sui dati di uscita del convertitore nel trasferimento | modalità di bus dati a 8 bit o bus dati a 16 bit. Quando il trasferimento del bus dati a 16 bit |

5 | è richiesta la modalità, mantieni questo pin logico alto, i dati lo saranno | trasferito nel bus, l'uscita del byte alto è nel pin da D1 a D8 (D1 è | 21 | bit alto) e il byte basso è da D9 a D16. Quando il trasferimento del bus dati a 8 bit | è necessaria la modalità, i dati sono ottenuti nei pin da D1 a D8 (disposti da high |

6 | a basso) e 8 bit alti e 8 bit bassi si ottengono in due tempi | sequenze, in altre parole, quando Byte select è alto logico, alto 8 bit | 22 | vengono emessi e quando è logico basso, vengono emessi 8 bit bassi. | Controllo blocco dati (segnale di inibizione) Inibizione |

7 | Questo pin è il pin di input della logica di controllo, la sua funzione è quella di output | dati esternamente al convertitore per realizzare latch o bypass opzionali | 23 | controllo. Ad alto livello, i dati di uscita del convertitore sono diretti | uscita senza latching, vedere il diagramma di sequenza temporale dei dati |

8 | trasferimento. A livello basso, i dati di uscita del convertitore sono bloccati, il | il ciclo interno non viene interrotto e il tracciamento rimane attivo per tutto il tempo | 24 | D1 | tempo, ma il contatore non emette dati. Quando è necessario trasferire |

9 | dati, il convertitore esegue prima il segnale di controllo Inhibit per bloccare i dati da alto a basso, mantiene la logica bassa per 640 ns, quindi imposta l'ingresso di abilitazione su basso (in questo momento il dispositivo occupa il bus dati), quindi | ottiene i dati tramite Byte select, quindi imposta tutte le logiche di controllo su high | 25 | D2 | per aggiornare e bloccare i dati in modo da essere pronti per il trasferimento |

10 | dati successivi, fare riferimento ai diagrammi di sequenza temporale del trasferimento dati Fig.4 | e Fig.5. | 26 | D3 | (3) Metodo di attenuazione del segnale di ingresso (Fig.4 e Fig.5) |

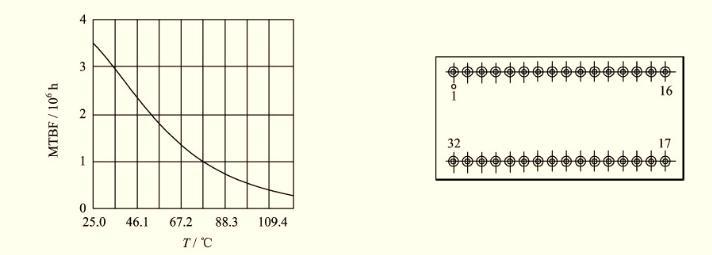

11 | Fig 4 Sequenza temporale del trasferimento del bus a 16 bit | Fig5 Sequenza temporale del trasferimento del bus a 8 bit | 27 | D4 | 6. Curva MTBF (Fig. 6) |

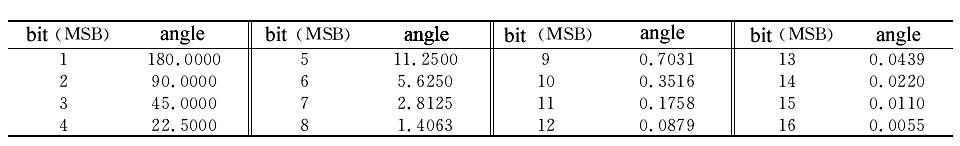

12 | Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1746) | 7. Designazione del perno (Fig.7, Tabella 4) | 28 | D5 | Convertitori da sincro a digitale o da resolver a convertitori digitali (serie HSDC/HRDC1746) |

13 | S3 | Fig.6 Curva temperatura MTBF | 29 | D6 | Fig.7 Designazione dei perni (vista dal basso) |

14 | S2 | (Nota: secondo GJB/Z299B-98, buone condizioni del terreno previste) | 30 | D7 | Tabella 4 Descrizione funzionale dei terminali dell'elettrocatetere |

15 | S1 | Spillo | 31 | D7 | Simbolo |

16 | NC | Significato | 32 | NC | Spillo |

Terra | D12 | Uscita digitale per 12 bit | -VS | -Alimentazione 15V | D13 | Uscita digitale per 13 bit | + Vs | Alimentazione +15V |

D14 | Uscita digitale per 14 bit | Ni | Inibire | Ni | Controllo del blocco dei dati | D15 | Uscita digitale per 15 bit |

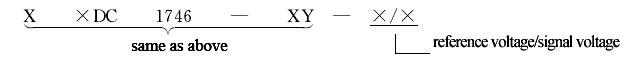

X

X